-

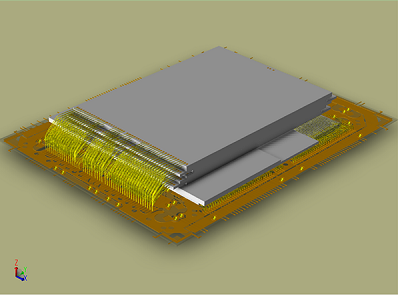

Allegro X Advanced Package Designer

市場對於更高功能性的需求推動了先進封裝的發展,以容納複雜的設計。要有效地設計這些複雜的封裝,需要一種能夠處理電氣和物理約束的高級實施工具。Cadence IC 封裝設計技術在全球範圍內被認可為高效、靈活且可靠的密集型先進封裝設計實施方案。集成的信號和電源完整性分析確保了在設計周期內,電氣和物理挑戰能夠共同解決。使用 Cadence IC 封裝設計技術,設計師能夠在有限的時間內實現一次到位。

IC 封裝現在已成為矽-封裝-電路板設計流程中的關鍵環節。Cadence Allegro 平台提供了完整且可擴展的技術,適用於 PCB 和複雜封裝的設計與實施。Cadence IC 封裝設計技術允許設計師在滿足短期項目時間表的同時,優化複雜的單晶片和多晶片引線鍵合及翻轉晶片設計,以達到成本和性能的平衡。

這種以約束為驅動的行業標準技術支持系統規劃、先進的 OSAT 和基於晶圓廠的封裝設計,從單晶片到複雜系統。Cadence IC 封裝設計技術提供高效的引線鍵合設計技術、考慮約束的基板互連設計,以及詳細的互連提取、建模和信號完整性/電源傳遞分析。

-

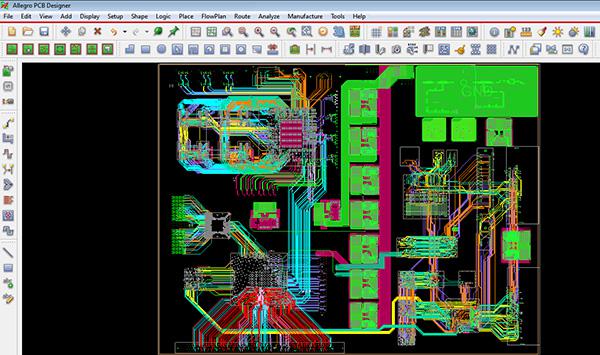

Allegro® PCB Designer

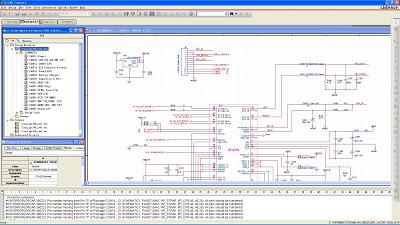

Cadence Allegro PCB Designer是一個完整的、高性能 PCB設計系統。通過頂尖的技術,它為創建和編輯複雜、多層、高速、高密度的印製電路板設計提供了一個互動式、約束驅動的設計環境。它允許用戶在設計過程的任意階段定義、管理和驗證關鍵的高速信號,並能解決今天最具挑戰性的設計問題。

-

CAMPro550 完整的PCB Layout檢查比對與DFM系統

CAMPro550 完整的PCB Layout檢查比對與DFM系統

PCB Layout 檢查、Open/Short檢查、比對、排版、DFM 檢測 -

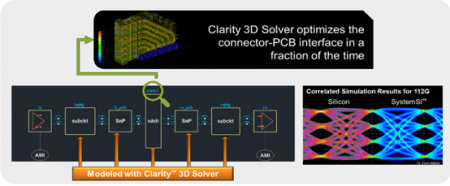

Clarity 3D Solver

Cadence Clarity 3D Solver 是一款 3D 電磁 (EM) 模擬軟體工具,用於設計 PCB、IC 封裝和 IC 系統 (SoIC) 設計的關鍵互連。 Clarity 3D Solver 可協助設計人員在設計 5G、汽車、高效能運算 (HPC) 和機器學習應用系統時以黃金標準精度應對最複雜的電磁 (EM) 挑戰。

Clarity 3D Solver採用了全新設計,透過平行化解決 3D 結構所需的矩陣計算,從而充分利用您的多核計算資源。這些任務可以在一台電腦的內核或多台電腦上平行處理,將解決複雜結構的時間縮短了 10 倍甚至更多。

Clarity 3D Solver創建高精度S 參數模型,用於高速訊號完整性(SI)、電源完整性(PI)、高頻射頻/微波應用和電磁相容(EMC) 分析,從而實現與實驗室測量相符的模擬結果,即使在 112Gbps+ 資料傳輸速度下也是如此。 Clarity 3D Solver 透過有效地將可用運算資源與設計尺寸相符來求解真正的 3D 結構。

-

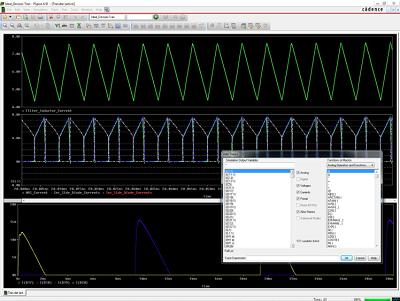

OrCAD PSpice Designer

OrCAD PSpice Designer和Advanced Analysis提供了業界領先的原理圖輸入,類比和數位混合信號完整的模擬和驗證解決方案。無論是製作簡單電路原型或者設計複雜系統,OrCAD PSpice Designer產品提供了最好的電路模擬技術,在進行PCB layout和生產之前可以幫助工程師分析和微調電路,以及元器

-

OrCAD Sigrity ERC

在電路板設計工具都有 Design Rule Check (DRC) 的幾何檢查功能,而Sigrity ERC (電氣規則檢查) 則擁有電氣規則檢查的功能,使PCB設計人員在沒有仿真模型或足夠的信號完整性專業能力的情況下,簡單而快捷地分析信號質量的問題和原因。

現今高速訊號設計越漸普及和額定工作電壓的降低,訊號完整性分析越顯重要,而SI分析需要較詳細的設定以及人員的經驗才可有效執行,Sigrity ERC / SRC是以電性規則進行 ERC 檢查和以批次模式進行 SRC 檢查,使PCB 設計人員在Allegro繪製電路板時,透過ERC檢查流程找出問題點或透過SRC得知嚴重程度,先行排除潛在問題,而不需要等完整的SI分析完成才進行修改,以減少SI人員為了確保最後的 SI 品質而配合多次的訊號分析,進而讓整體設計時程能夠縮短。

-

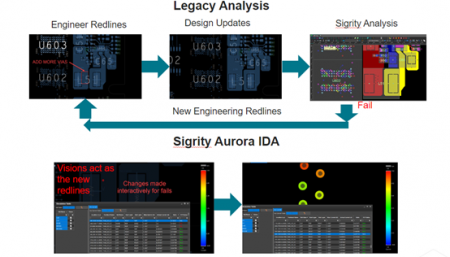

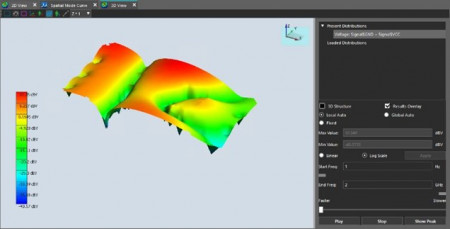

Sigrity Aurora

Cadence Sigrity Aurora為佈局前、設計中、以及佈局後的 PCB 設計提供設計同步訊號和電源完整性(SI/PI)分析,結合Cadence Allegro® PCB編輯和佈線技術,Sigrity Aurora 用戶能夠在設計週期的早期,從而實現精確的「假設」場景規劃,以設定更準確的設計約束並最大限度地減少設計迭代。

由於Sigrity Aurora可以直接讀寫Allegro PCB資料庫,因此能快速準確地整合設計與分析結果。提供基於 SPICE 的模擬器和 Sigrity 專利的嵌入式混合場求解器,提取 2D 和 3D 結構。若需要,可支援Power-Aware的IBIS(行為)模型,並且也支援電晶體等級的模型。高速訊號可以在佈局階段或佈局後,對比較備選方案進行研究,以便對所有相關訊號進行全面分析。

直流電源完整性(PI)分析可以測量電源和接收器之間的任意電壓降。其結果可在設計視窗中以電壓、壓降、或電流密度的視覺化方式呈現。設計人員透過改變設計,並迅速查了解設計改變造成的影響,而不必離開Allegro PCB設計介面。

-

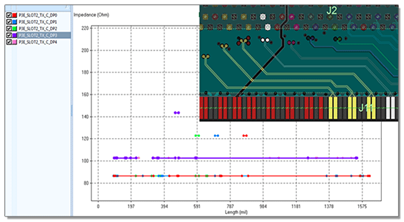

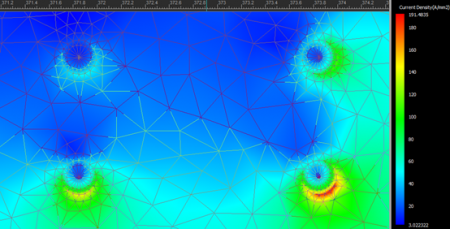

Sigrity PowerDC

PowerDC技術為 IC封裝和 PCB設計的簽核提供高效的 DC分析,是一款經典的電熱協同模擬工具,模擬條件考慮了電流與溫度之間的相互作用影響,整個電路板的直流電壓降,電流密度分佈,溫度熱量分佈以及所有貫孔通過電流的情況,基於仿真結果,提供自動化的智能選擇理想 VRM 感線的位置,使設計產品良率大大提高。

PowerDC流程化的自動規則檢查功能,並結合可視化的選項與DRC規則檢查,確保了各裝置端到端的電壓降裕量,進而確保電源網路的穩定供應。同時也能快速偵測定位電流密度超標、溫度超標的區域進而降低產品的風險。

-

Sigrity PowerSI

由於耦合、電源、接地反彈所造成的同步開關輸出等等,皆是造成信號品質的元兇,PowerSI利用獨特的電磁混合模擬引擎能夠有效率且準確地為設計人員擷取訊號或電源平面的網路參數(S/Y/Z),涵蓋頻段從DC至Ghz,並進行空間模式下的雜訊分佈及本徵結構的諧振模式分析。

PowerSI 為 Cadence 獨特的專利分析技術,使用了精準的網格模擬方式,將複雜的設計簡單化,進而計算複雜的結構設計,於積體電路 (IC) 封裝與印刷電路板 (PCB)提供快速、精確的波電力分析,現今工程師設計的產品皆會遇到 EMI、電源功率、信號完整性、近場和遠場輻射的問題,透過PowerSI 可有效率的下解決方案,使工程師可輕鬆有效率地分析和調整自己的設計。

公司電話:+886-3-271-1599