描述

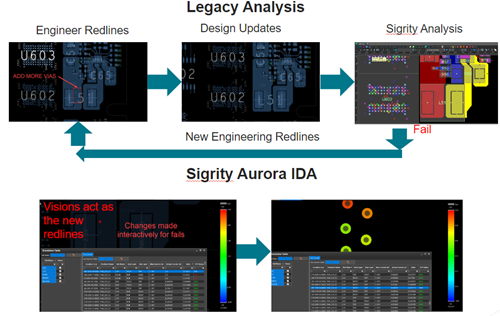

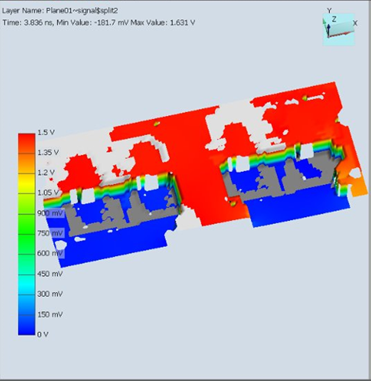

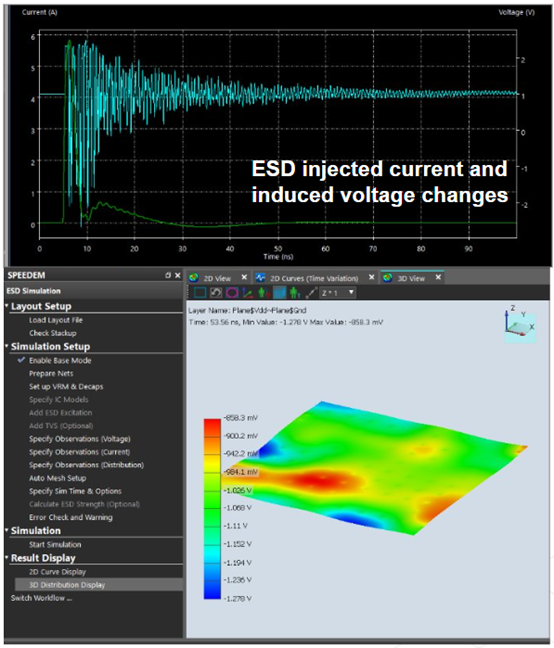

SPEEDEM 可支援 IBIS 和 SPICE 模型,且因結合了電路與傳輸線的模擬,使用全波電磁場的方式運算,在運算時間上相當快速。模擬時為使用者考慮各種實際的非理想因素,如平面破碎、高密度過孔、走線之間的耦合以及返回路徑的不連續性等,並將訊號完整性與電源完整性同時考慮,模擬出真實的SSO,得到基於實際工作狀況下所有訊號線的時域波形。

產品特點

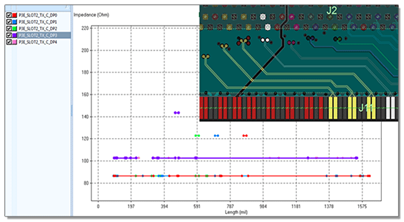

- 工作流程還包括互連模型擷取、時域反射 (TDR)、時域傳輸 (TDT) 和電源漣波分析

- 獨特的電磁相容 (EMC) 模擬解決方案,支援非線性驅動器和接收器

- 確定層疊、平面幾何形狀和 I/O 配置變化的影響

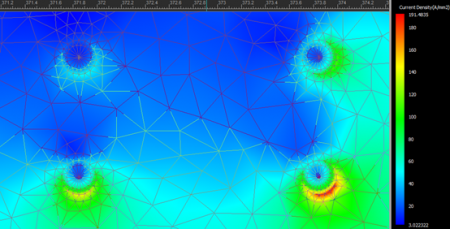

- 觀察噪音的產生,識別其傳播方式,並確定其是否保持在目標規範內

- 為外部電路模擬器(例如 Sigrity SystemSI 工具)擷取單一或耦合訊號線的互連模型

- 用作 Sigrity SystemSI FDTD 直接引擎,用於系統級功耗感知 SI 分析 (無需 S 參數)

- ESD 工作流程提供有關 TVS 二極體有效性的回饋

- 針對 Allegro X 設計平台、Allegro X 高級封裝設計平台以及 Mentor、Zuken 和 Altium 流程進行了最佳化,接受多種結構設計支援所需的 CAD 資料庫混合