描述

Cadence OrCAD Capture是一款簡單易用、功能特點豐富的電路圖繪製工具。由於它簡單直觀的使用模式和易用性使其成為全球最受歡迎的設計輸入工具。同時具有元件資訊管理系統(CIS)可以線上訪問或從中心元件資料庫中調用元器件符號,可以極大的提高電路圖的繪製效率。無論是創建新的類比電路、修改現有的PCB設計電路圖或是繪製層次模組的方框圖,OrCAD Capture提供了工程師設計電路所需要的全部功能。電路圖輸入工具OrCAD Capture、PCB Layout設計工具OrCAD PCB Editor和數模混合模擬工具PSpice A/D之間實現無縫連結,確保電路設計的高效率運作。OrCAD Capture結合Component Information System(CIS)的功能,使得工程師可以隨時訪問大量線上的元器件符號、也易於查看元器件的各種資訊。

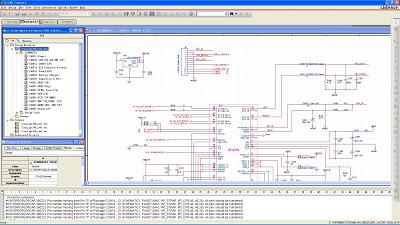

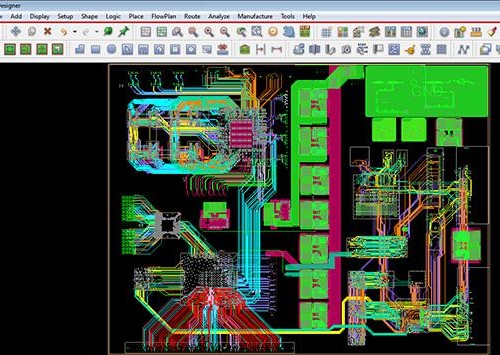

電路圖編輯器

OrCAD Capture層次式和拼接式電路繪製方式繼承了OrCAD傳統電路圖簡單易用的設計特點。它將簡單直觀的介面和快速創建電路的功能相結合。對於大規模複雜電路設計,OrCAD Capture支援拼接式和層次式的電路設計,更有利於層次式電路設計的切換以確保整個設計的連貫性和準確性。

易用性

直觀的使用者介面,結合16.3版本的改進功能滿足了快速繪製且提高設計效率的要求。例如:自動連線功能,引腳間的佈線通常是一項乏味的工作,該功能實現了從一個引腳到另外一個引腳的自動快速添加連接線。功能表中OLE提供了導線/網路/元件的色彩自訂,利用表單介面方式為使用者提供了更好的視覺體驗。

設計重用

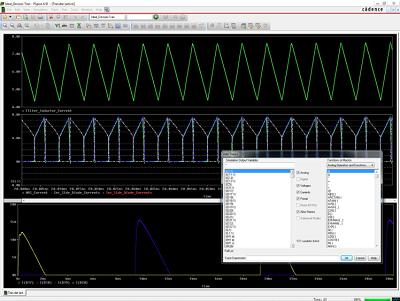

設計複用可以大大減少設計階段,提高設計品質。對於已經擺放及連線完成且通過驗證的電路可以直接被覆用到現有設計中去。典型的設計重用案例有開關電源模組、RF電路設計模組、多通道電路模組(I/O、驅動程式等)、記憶體電路模組等。

設計規則檢測

OrCAD Capture具有可選擇的設計規則檢查(DRC)功能,在進行後續設計前要進行全面檢查電路圖是否違背DRC設計規則,以縮短設計週期並減少設計反復的各種成本。設計規則檢查包括冗餘元件檢查,無效封裝和電氣規則衝突檢查等。

元件資訊系統

元件資訊系統(CIS)是OrCAD Capture設計解決方案的核心部分,它可以自動同步和檢驗電路圖設計中的元件和相關聯的優選元件資料庫。CIS與微軟ODBC元件資料庫相容,能夠直接調用存儲在MRP,ERP或PLM系統以及工程資料庫中的元件資訊。相關資料支援CIS允許創建和使用關聯式元件資料庫表格,這些關聯式表格與元件資訊表格是一對多的關係。關聯式資料可能包含多個供應商/製造商的元件編號(如電阻元件編號表)。基於這種資料結構,沿著這些關聯式資料表格搜索和查詢元件變成可能。

元件調用

元件資料和器件資訊在CIS中可以很方便的進行查詢,設計師可以大大減少查找器件的時間。元件資訊系統(CIS)的內置系統用於創建、跟蹤和認證元件,可以使用任意屬性組合作為元件搜索條件。當設計師調用一個元件後,CIS會提取該元件的所有相關技術資料,包含電氣、物理、功能、採購以及製造特性,然後在電路圖頁面上可以對其進行檢索。設計師如果直接從企業資料庫(CIS)中添加元件,可以最大限度的減少產生元件報表和生成元件清單的錯誤,還可以設定元件的工業標識,例如RoHs和WEEE。

互聯網元件助理

CIS還可以通過互聯網元件助理(ICA)訪問網路資料庫的元件資訊。由於訪問的是企業資料庫,所以可以在網路上查詢元件的電氣,物理和製造性能,在電路圖中可以對其進行編輯和檢索。ICA包含了免費的Cadence ActiveParts線上電子元件資料庫,有200多萬個元件資訊可供使用。ActiveParts用戶可以搜索和選擇具體的元件,並在擺放到電路圖前進行預覽。

同一電路圖不同機型

BOM表的生成

Orcad Capture支持同一電路圖不同機型BOM表的生成功能,這樣設計師不必重複維護電路圖副本及手動編輯BOM表。基於同一電路圖,設計師可以匯出多個裝備機型的BOM表。FPGAOrCAD Capture和OrCAD FPGA Systerm Planner結合使用來解決工程師在PCB電路板上設計多引腳數的FPGA時遇到的創建初始引腳分配,確保板子的走線等問題。FPGA-PCB協同式設計提供了一個完整的、可升級的技術,以及最佳引腳分配規則,符號創建和流通的“設計規則精細化”的自動創建。通過手動修復自動引腳分配和易出錯過程,解決並消除了不必要的重複設計,並縮短創建最佳引腳分配的時間。

Capture環境中FPGA創建

OrCAD Capture支援FPGA設計的快速導入功能和創建FPGA符號和元件。隨著不斷增加的引腳數和FPGA元件的複雜度,通常使用以GUI為基礎的OrCAD Capture創建一個或多個基於FPGA元件I/O元件的引腳檔。Capture也具有分割元件功能,依據設計需要,可以靈活設置電源管腳顯示、管腳形狀、為管腳群組管理。FPGA元件也可以採用FPGA對話方塊輸出,FPGA輸出可以在FPGA和PCB設計之間實現雙向連接。

協同設計

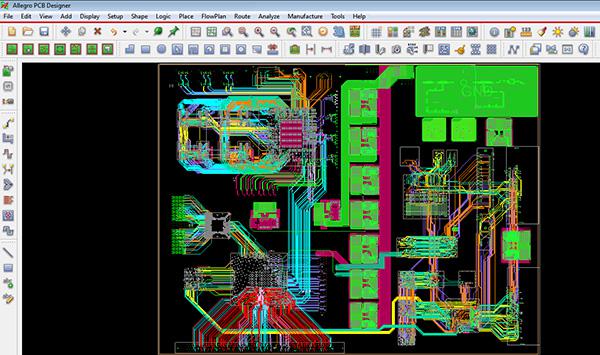

OrCAD FPGA System Planner為FPGA-PCB協同式設計提供了一個完整的解決方案,允許用戶創建最優的FPGA準確式結構引腳分配。FPGA引腳的自動分配是基於使用者指定,連接基礎介面,結合FPGA引腳分配規則和在PCB上進行實際佈線。自動引腳整合技術避免用戶手動中易錯的過程並縮短了FPGA在PCB設計佈線創建初期引腳分配的時間(引腳位置預測)。這種獨特的引腳位置預測分配方法消除了手工方法中不必要的物理設計反覆運算次數。OrCAD FPGA System Planner綜合了OrCAD Capture和OrCAD PCB Editor,它可以讀取和創建OrCAD Capture電路圖和封裝。此外,OrCAD PCB Editor平面視圖會顯示存在的封裝庫。在佈局時可以修改佈線,可以從OrCAD PCB Editor直接訪問FPGA System Planner引腳進行最佳化分配使用。

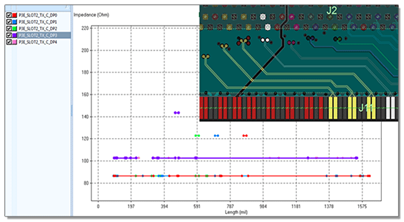

OrCAD PCB流程

OrCAD PCB Editor的無縫雙向整合技術可以實現電路圖與電路板之間的同步互動式佈局,使兩者始終保持一致。自動工程變更指令(ECOs)可在進行任意元件的引腳互換、門互換,以及元件名稱或參數發生改變時及時反標回電路圖輸入工具。OrCAD Capture CIS自帶一個電路圖元件符號庫,它具有VHDL模組,EDIF電路圖和其它CAD廠商對應的網表介面。