Sigrity

-

Sigrity PowerSI

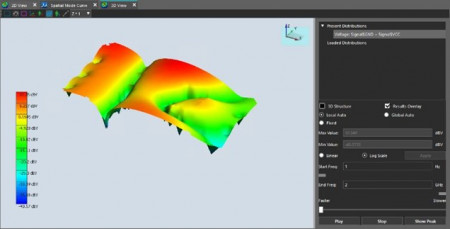

由於耦合、電源、接地反彈所造成的同步開關輸出等等,皆是造成信號品質的元兇,PowerSI利用獨特的電磁混合模擬引擎能夠有效率且準確地為設計人員擷取訊號或電源平面的網路參數(S/Y/Z),涵蓋頻段從DC至Ghz,並進行空間模式下的雜訊分佈及本徵結構的諧振模式分析。

PowerSI 為 Cadence 獨特的專利分析技術,使用了精準的網格模擬方式,將複雜的設計簡單化,進而計算複雜的結構設計,於積體電路 (IC) 封裝與印刷電路板 (PCB)提供快速、精確的波電力分析,現今工程師設計的產品皆會遇到 EMI、電源功率、信號完整性、近場和遠場輻射的問題,透過PowerSI 可有效率的下解決方案,使工程師可輕鬆有效率地分析和調整自己的設計。

-

Sigrity PowerDC

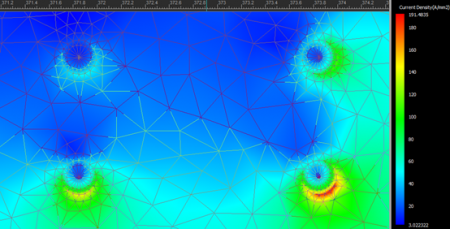

PowerDC技術為 IC封裝和 PCB設計的簽核提供高效的 DC分析,是一款經典的電熱協同模擬工具,模擬條件考慮了電流與溫度之間的相互作用影響,整個電路板的直流電壓降,電流密度分佈,溫度熱量分佈以及所有貫孔通過電流的情況,基於仿真結果,提供自動化的智能選擇理想 VRM 感線的位置,使設計產品良率大大提高。

PowerDC流程化的自動規則檢查功能,並結合可視化的選項與DRC規則檢查,確保了各裝置端到端的電壓降裕量,進而確保電源網路的穩定供應。同時也能快速偵測定位電流密度超標、溫度超標的區域進而降低產品的風險。

-

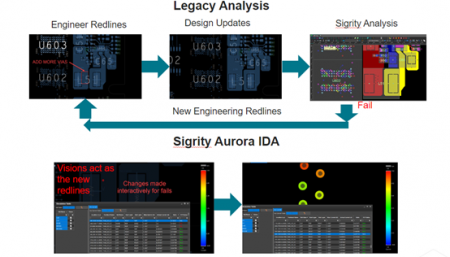

Sigrity Aurora

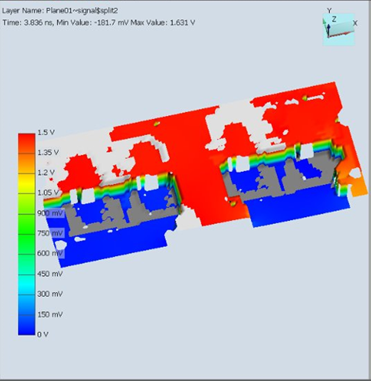

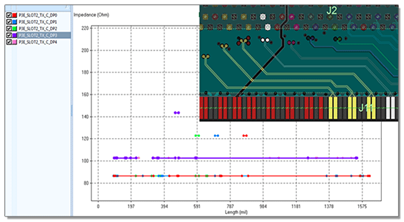

Cadence Sigrity Aurora為佈局前、設計中、以及佈局後的 PCB 設計提供設計同步訊號和電源完整性(SI/PI)分析,結合Cadence Allegro® PCB編輯和佈線技術,Sigrity Aurora 用戶能夠在設計週期的早期,從而實現精確的「假設」場景規劃,以設定更準確的設計約束並最大限度地減少設計迭代。

由於Sigrity Aurora可以直接讀寫Allegro PCB資料庫,因此能快速準確地整合設計與分析結果。提供基於 SPICE 的模擬器和 Sigrity 專利的嵌入式混合場求解器,提取 2D 和 3D 結構。若需要,可支援Power-Aware的IBIS(行為)模型,並且也支援電晶體等級的模型。高速訊號可以在佈局階段或佈局後,對比較備選方案進行研究,以便對所有相關訊號進行全面分析。

直流電源完整性(PI)分析可以測量電源和接收器之間的任意電壓降。其結果可在設計視窗中以電壓、壓降、或電流密度的視覺化方式呈現。設計人員透過改變設計,並迅速查了解設計改變造成的影響,而不必離開Allegro PCB設計介面。

-

Sigrity SPEEDEM

Sigrity SPEEDEM 技術使用基於佈局的時域有限差分 (FDTD) 仿真,為綜合訊號、電源、EMI 和 ESD 研究提供整合環境。 這項創新工具將電路和傳輸線模擬與高速、專用電磁(EM)場解算器無縫結合起來,動態分析IC 封裝以及電路板訊號和平面上的訊號、電源和接地之間的相互作用,確保快速、精確的結果。

-

OrCAD Sigrity ERC

在電路板設計工具都有 Design Rule Check (DRC) 的幾何檢查功能,而Sigrity ERC (電氣規則檢查) 則擁有電氣規則檢查的功能,使PCB設計人員在沒有仿真模型或足夠的信號完整性專業能力的情況下,簡單而快捷地分析信號質量的問題和原因。

現今高速訊號設計越漸普及和額定工作電壓的降低,訊號完整性分析越顯重要,而SI分析需要較詳細的設定以及人員的經驗才可有效執行,Sigrity ERC / SRC是以電性規則進行 ERC 檢查和以批次模式進行 SRC 檢查,使PCB 設計人員在Allegro繪製電路板時,透過ERC檢查流程找出問題點或透過SRC得知嚴重程度,先行排除潛在問題,而不需要等完整的SI分析完成才進行修改,以減少SI人員為了確保最後的 SI 品質而配合多次的訊號分析,進而讓整體設計時程能夠縮短。

-

Sigrity SI/PI Analysis Overview

Companies designing complex PCBs are faced with power integrity (PI) and signal integrity (SI) issues driven by increasing data transmission rates combined with decreases in power-supply voltages and denser, smaller geometries.