DDR5 UDIMM 至 Clock Buffered DIMMs (CUDIMM) 的演進

DDR5是新一代的 PC DDR 記憶體,廣泛應用於數據中心、筆記型電腦、個人電腦、自駕系統、伺服器、雲端運算和遊戲等領域,隨著記憶體帶寬和密度的進步,現在越來越多地被用於人工智慧應用。DDR5 DIMM(雙列直插記憶體模組)可以支持每個 DIMM 卡超過 256 GB 的更高密度。最高速度的 DDR5 SDRAM設備可支持高達 8800 MTps 的數據傳輸速率。

DDR5 SO-DIMMs and UDIMMs

PCDDR 最為人所知的應用之一是在客戶端設備,如筆記型電腦和個人電腦中。這些客戶端設備主要使用兩種類型的 DDR5 DIMM,分別是 SO-DIMM(小型輪廓雙列直插記憶體模組)和 UDIMM(無緩衝雙列直插記憶體模組)。

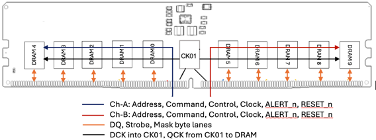

這些類型的 DIMM 沒有信號再生或緩衝(例如,註冊 DIMM 的Clock/命令/控制信號是由註冊Clock驅動器(RCD)進行處理的)。典型的 2 排 UDIMM,使用 x8 DDR5 SDRAM 元件,每排有 8 或 10 個元件,具體取決於系統是否使用 ECC(錯誤更正碼)記憶體。

Why DDR5 Clock Buffer and CUDIMM?

Clock是同步設備中最重要的信號之一,DDR5 SDRAM 也不例外。主機負責將Clock信號分配到所有 DRAM 輸入端口,例如 UDIMM 的Clock。驅動這些 DRAM Clock會對主機輸出驅動器造成相當大的負載,從而影響信號質量,這可能導致意外的記憶體錯誤。當操作於更高的Clock和數據速率時,這個問題會更加嚴重,因為Clock信號會在極短的時間內從一個邏輯值過渡到另一個邏輯值。為了解決這些 DRAM Clock的信號完整性問題,JEDEC 提出了新型的 DDR5 DIMM 元件,即 DDR5 Clock緩衝器。Clock緩衝器可以用於 DDR5 SO-DIMM 和 DDR5 UDIMM。包含Clock緩衝元件的 DDR5 UDIMM 被稱為 DDR5 CUDIMM(Clock緩衝 UDIMM)。

DDR5 Clock Buffer Overview

DDR5 Clock緩衝器是一種簡單的邏輯設備,它接受兩組輸入Clock引腳並驅動每個通道的兩組輸出Clock引腳。Clock緩衝器設備可以在三種Clock模式下運行:

-

- PLL 繞過模式:在此模式下,Clock緩衝器僅將輸入Clock傳遞至輸出,沒有任何形式的信號緩衝。 啟用 PLL 繞過模式的 CUDIMM 設備行為類似於傳統的 UDIMM,沒有Clock緩衝。因此,它也被稱為傳統模式。推薦的 CUDIMM 操作速度在 PLL 繞過模式下通常限制為 3000 MHz。

- 單 PLL 模式:在單 PLL 模式中,Clock緩衝器設備將使用相位鎖環(PLL)來再生進來的主機Clock,創建更高質量的Clock並將其發送到 DRAM。但是,由於此模式中僅使用一個 PLL,因此兩個子通道的輸出Clock將僅基於一組輸入Clock來驅動,另一組輸入Clock將保持未使用狀態。

- 雙 PLL 模式:在此模式下,Clock緩衝器將使用兩個 PLL 獨立生成每個子通道的輸出Clock,根據每組進來的主機Clock。第二組 PLL 可以根據需要動態開啟或關閉,以節省功耗。

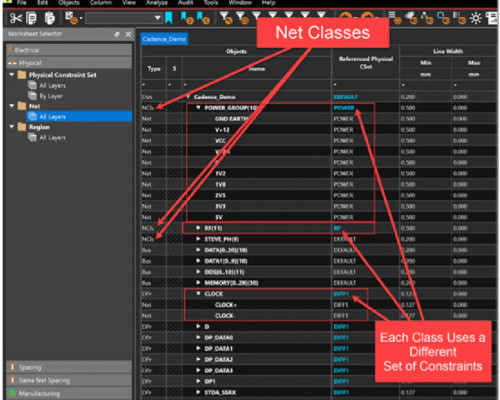

除了Clock模式外,Clock緩衝器還為系統設計師提供了更多的靈活性,例如寄存器控制的額外信號延遲、每位可選的輸出Clock啟用/禁用功能、驅動強度和終端選擇等。所有 DDR5 Clock緩衝器設備的控制字寄存器可以通過 DDR5 DIMM 邊帶訪問。

Cadence VIP 提供了一個全面的記憶體子系統解決方案,其中包括 DDR5 SDRAM、DDR5 RCD、DDR5 DB、DDR5 Clock緩衝器、所有類型的 DDR5 DIMM(包括 DDR5 CUDIMM)、DFI 記憶體控制器/PHY VIP、以及符合 JEDEC 規範的系統 VIP,這些規範針對每個設備及最新的 DFI 規範進行了定義。

請參考出處:原始文章連結